eetiems 湯之上氏

↓

湯之上氏の解説なので内容が専門的になっています。eetimesにCoWosの技術についてのレポートがあります。

<用語について。。>

************* ①CoWoS *************

↓

++++++++++ 適宜 貼り付けます。

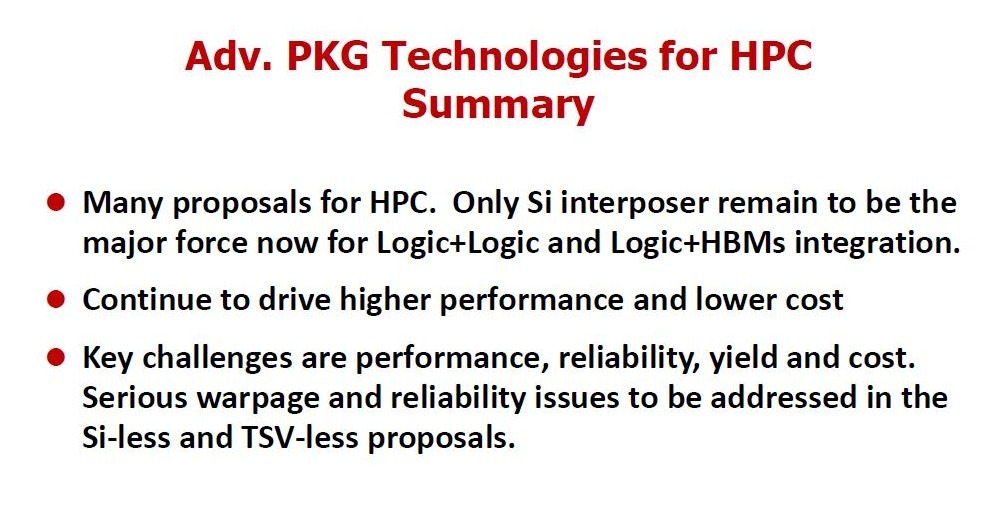

CoWoS技術の本質は、シリコンダイを近接して並べることで、プリント基板における占有面積を減らすこと、言い換えると半導体チップの実装密度を高めることにある。従来は、半導体デバイスはシリコンダイを樹脂封止した状態で、プリント基板に個別に実装するのが普通だった。隣接する半導体チップ(シリコンダイ)の間隔は短くても、20mmくらいの長さがあった。実配線長はさらに長くなる。50mm前後の長さは珍しくない。

CoWoS技術ではシリコンインターポーザの導入により、隣接するシリコンダイの距離をわずか0.03mm(30μm)にまで詰められる。数GHzあるいは数Gビット/秒と高周波・高速の信号伝送を可能とする

CoWoS技術によるパッケージ製造(組み立て)の特徴は、直径が300mmあるいは200mmといったシリコンのウエハーを扱うことにある。大量のパッケージを一括して製造するので、組み立てのコストが下がる。

^^^^^^^^^^^^^^^

CoWoS技術の問題点は装置コスト(初期コスト)にある。ウエハーとキャリアを扱う工程が増えるので、装置コスト(初期コスト)が上昇する。一定の数量が見込めないと、CoWoS技術は採用しづらい。ただし、いったん設備を導入してしまうと、パッケージ1個当たりの製造コスト(ランニングコスト)はCoWoS技術の方がCoCoS技術よりも低くなる。一定の生産数量が確保できれば、初期コストを回収できる時期は早ま

^^^^^^^^^^^^^^^^^

る。

++++++++++

3階層の接続構造を採るCoWoS技術のパッケージングの歩留まりの悪さに問題がありそうです。。コスト回収をするには数が必要なようです。(投資回収が出来る事がカギになりそうです。)

************ ②HBM(High Bandwidth Memory) ********

↓

昨今メモリを巡る状況は広帯域化へと進んでいます。微細化加工の限界もあるようです。1nm刻みの微細化って。。凄い事だと思います。

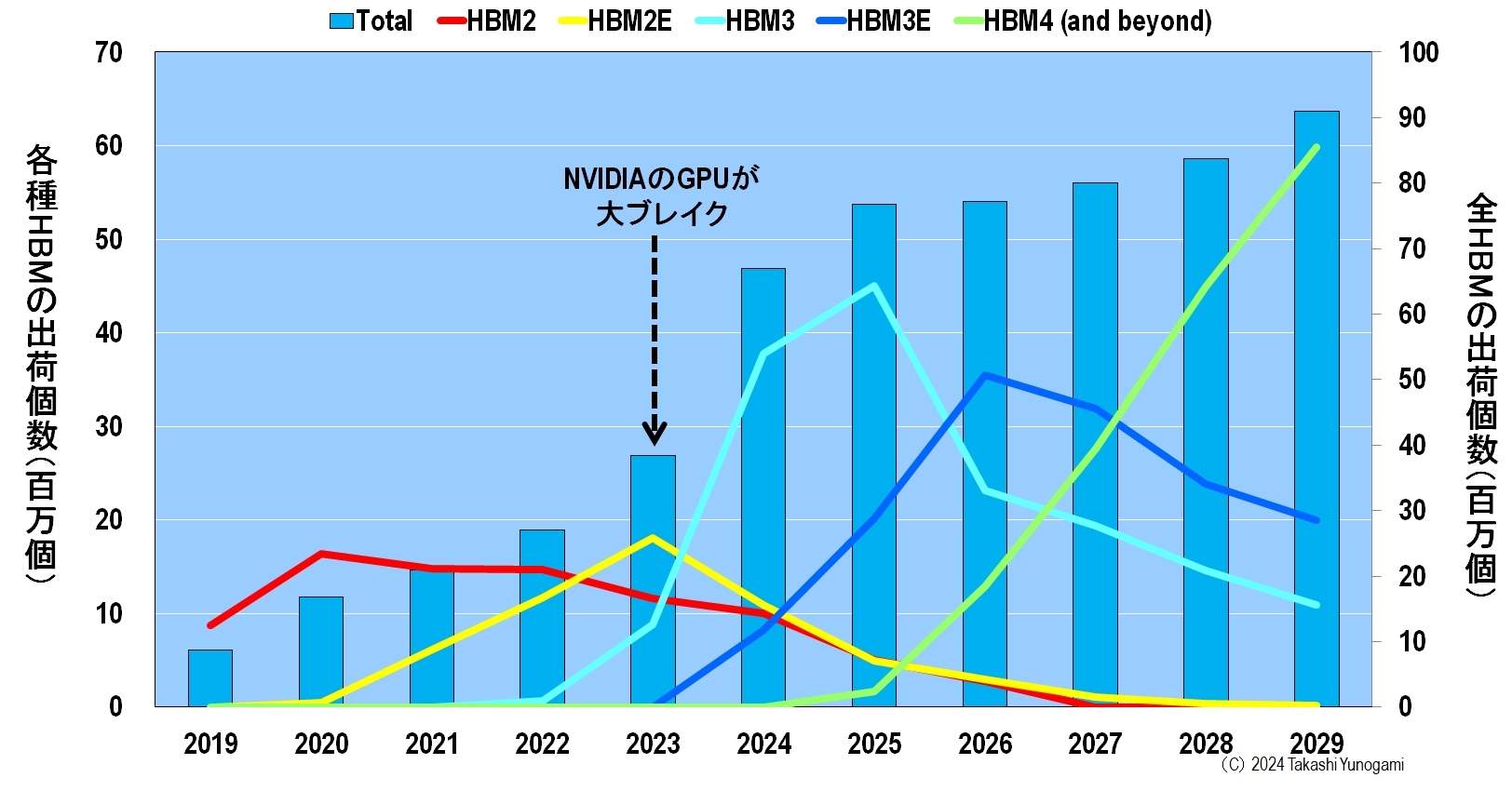

Samsung SK hynix Micron と各社がしのぎを削っているようですが、DRAMにEUVを使用したのはSamsung SK Hynix ですが、MicronはEUV無しで頑張ってきましたようです。。が、最終的には導入する見通しのようです。GPUに広帯域メモリは必須です。

マイクロンが広島に工場を作るのはこのためか。。判った。

↓

既に、1βノードDRAMは広島で量産しています。

CoWoSパッケージの製造工程の限界。HBMの不足。が足を引っ張っているようです。湯之上氏の主張によればGPUは今後も不足するとの予想です。

EUVはXXX億円(三桁)は必要です。それも製造ラインに複数台必要でしょう。ASMLは儲かりますが。。EUVだけでXXXX億円必要となってきます。

東京エレクトロン

↓

いや~。。いくらお金があっても足りないぐらいです。各国が国家プロジェクトとして取り組むわけです。。後は投資回収です。。AIブームが今後とも現在の調子で進む必要があります。そこまで先の事は予想出来ません。更なる微細化が待ち構えています。(同時に困難も待ち受けています。)何処かが根を上げそうな気がします。