※ 投稿中にネットがハングったりしたために、中途半端なものを連投してしまいました。

それと、最後の回路図は間違っています。直すかどうか考慮中。

フリップフロップに関して、取り上げ損ねたものが一つあった。ネタか!?という問題のような気がして最初私には答えが分からなかったというものである。

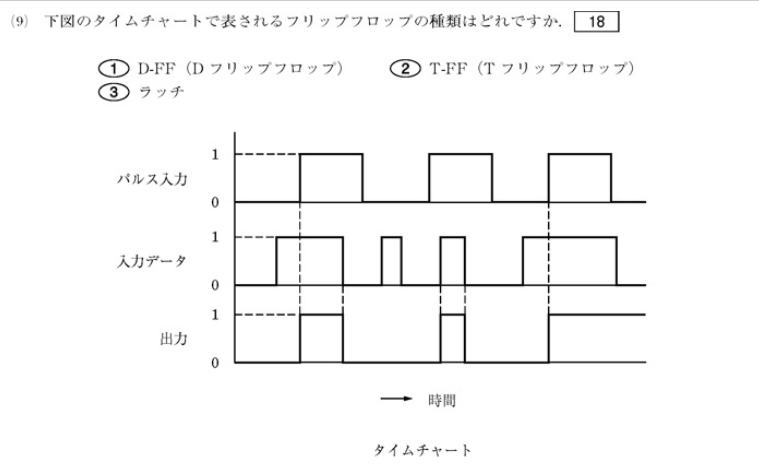

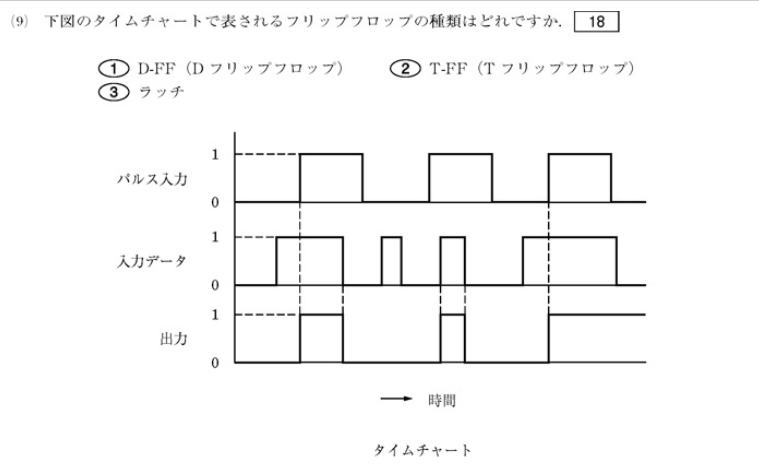

下図はディジタル技術検定 3 級第 49 回の (9) である。

最初タイムチャートの意味が分からなかった。で、消去法で考えることにした。まず除けるのが(2)の T - FF で、これはその機能から入力は一つしかない(リセット、セットは除く)ので違うだろう、ということで除外。(1)の D - FF はパルス入力をクロックと考えると、入力信号の数はあっている。その場合は入力パルスの立ち上がりもしくは立ち下がりのタイミングで出力が変化しなくてはいけない。しかし出力はそういう動作になっていない。よってこれも違う。そうすると残り(3)ラッチということになるのだが、まずラッチというなら入力端子は「セット」「リセット」になっているはずだし、それでは答えがバレバレなので少なくともそれぞれを同レベルに扱う「入力1」「入力2」として欲しいものだ。

で、文句を言いながらも下図のように入出力に変化がある毎に番号(以下 T* とする)を振っていって一つ一つ見ていくことにする。ついでに各タイミング毎を表にしてみた。

T0 では「パルス入力」(以下 Pls)も「入力データ」(以下 Data)も '0' で出力は '0'、これはそういうものかと T1 で Data が '1' になっても出力は変わらず、T2 での Pls の立ち上がりで出力が '1' に変わるから、Pls と Data は何らかの論理で出力に影響を与えていることが分かる。で、T3に Data が '0' になると Pls は '1' のままなのに、出力は '0' になっているから、ここまでだけ見ると単なる Pls と Data の AND ゲートに見える。さらにその論理で説明がついてしまう状態は T12 まで続いている。つまり出力が T13、T14 で '1' のままになっている以外は AND ゲートで実現できてしまう。これは表の青線で示している。赤点線は同じ状態が 2 度現れていることを示してみた。では、どうすれば最後に '1' のままでいられるような論理ないしはフリップフロップを組むことができるのか。

どうやら、Pls は Data が '1' の時に立ち上がりで出力を '1' にすることが出来て、Data は Pls が '1' の時に立ち下がりで出力を '0' にすることができるという論理 + ラッチになっているようだ。

無理矢理回路を組んでみると以下のような回路になっていそうである。

これは FPGA を作るツールで書いたものだが残念ながらテストベンチは作っていないので検証はできない。余力のあるときにでもやってみようとは思っている。

ちなみにタイムチャートに紫色で線を付け加えているが、これだったら単純な R - S で実現できる。が、AND ゲートでも実現できるあたりが腹立たしい。

こんな回路を想定して(3)と選ぶことになるのだが、本当に出題者の意図通りなのかよく分からない。

3 級の過去問題をお持ちの方は、この問題の解答と解説を教えてくれると有り難いです。

← にほんブログ村「科学」-「技術・工学」へ

← にほんブログ村「科学」-「技術・工学」へ

↑ クリックをお願いします。

それと、最後の回路図は間違っています。直すかどうか考慮中。

フリップフロップに関して、取り上げ損ねたものが一つあった。ネタか!?という問題のような気がして最初私には答えが分からなかったというものである。

下図はディジタル技術検定 3 級第 49 回の (9) である。

最初タイムチャートの意味が分からなかった。で、消去法で考えることにした。まず除けるのが(2)の T - FF で、これはその機能から入力は一つしかない(リセット、セットは除く)ので違うだろう、ということで除外。(1)の D - FF はパルス入力をクロックと考えると、入力信号の数はあっている。その場合は入力パルスの立ち上がりもしくは立ち下がりのタイミングで出力が変化しなくてはいけない。しかし出力はそういう動作になっていない。よってこれも違う。そうすると残り(3)ラッチということになるのだが、まずラッチというなら入力端子は「セット」「リセット」になっているはずだし、それでは答えがバレバレなので少なくともそれぞれを同レベルに扱う「入力1」「入力2」として欲しいものだ。

で、文句を言いながらも下図のように入出力に変化がある毎に番号(以下 T* とする)を振っていって一つ一つ見ていくことにする。ついでに各タイミング毎を表にしてみた。

T0 では「パルス入力」(以下 Pls)も「入力データ」(以下 Data)も '0' で出力は '0'、これはそういうものかと T1 で Data が '1' になっても出力は変わらず、T2 での Pls の立ち上がりで出力が '1' に変わるから、Pls と Data は何らかの論理で出力に影響を与えていることが分かる。で、T3に Data が '0' になると Pls は '1' のままなのに、出力は '0' になっているから、ここまでだけ見ると単なる Pls と Data の AND ゲートに見える。さらにその論理で説明がついてしまう状態は T12 まで続いている。つまり出力が T13、T14 で '1' のままになっている以外は AND ゲートで実現できてしまう。これは表の青線で示している。赤点線は同じ状態が 2 度現れていることを示してみた。では、どうすれば最後に '1' のままでいられるような論理ないしはフリップフロップを組むことができるのか。

どうやら、Pls は Data が '1' の時に立ち上がりで出力を '1' にすることが出来て、Data は Pls が '1' の時に立ち下がりで出力を '0' にすることができるという論理 + ラッチになっているようだ。

無理矢理回路を組んでみると以下のような回路になっていそうである。

これは FPGA を作るツールで書いたものだが残念ながらテストベンチは作っていないので検証はできない。余力のあるときにでもやってみようとは思っている。

ちなみにタイムチャートに紫色で線を付け加えているが、これだったら単純な R - S で実現できる。が、AND ゲートでも実現できるあたりが腹立たしい。

こんな回路を想定して(3)と選ぶことになるのだが、本当に出題者の意図通りなのかよく分からない。

3 級の過去問題をお持ちの方は、この問題の解答と解説を教えてくれると有り難いです。

↑ クリックをお願いします。