下図はディジタル技術検定 3 級第 52 回の (9) である。

フリップフロップ(Flip-Flop)を使った非同期カウンタの問題で、フリップフロップが 4 つあるのでいわゆる 4 bit カウンタである。

ここで使われているフリップフロップは T フリップフロップといって、T' 端子に下降信号(立ち下がりエッジ)が入ると出力が反転するものである。仮に 4 つのフリップフロップの初期値を (0000) とすると、一番左の入力パルスの立ち下がり信号が入ると Q0 が反転して '1' になる。他のフリップフロップの T' は変化していないので出力は変わらない。よって (0000) → (1000) と変化する(普通の表記と上位と下位が逆になっていることに注意)。次に入力パルスの立ち下がりがあると、Q0 は '0' になる。このためその右のフリップフロップには '1' から '0' に変化した信号が入力されるので、Q1 の出力は反転して '1' になる。Q2, Q3 は変化しないので、(0100) となる。以下同様にパルスを与えていくと、Q0, Q1, Q2, Q3 は順次変化していくが Q1 と Q3 が同時に '1' になると NAND を通して、各フリップフロップのリセット端子に '0' を出力して、Q0, Q1, Q2, Q3 をすべてリセット = (0000) にしてしまい、初期値に戻る。よって、(0000) から (0101) まで変化して元に戻るので、0 から 10 まで数えたところで 0 に戻るということで、(4)の 10 進カウンタが正解となる。0 から 10 なら 11 個数えたことになるのでは?と思うかも知れないが、(0101) となった瞬間に次のパルスが入る前に (0000) に戻ってしまうので、10 は数えたことにしない。変な感じだが、非同期カウンタはこういう動作をすることが多い。

参考までにタイミングチャートはこのようになる。(0101) になった期間が短くすぐに (0000) になっている。

余談だが、T が負論理 T' になっていて入力パルスの立ち下がりに反応するようになっているのは、もしこれを立ち上がりに反応するようにすると、Q0 が '1' になった瞬間にその立ち上がりに反応して Q1 が '1' になり、それを受けて Q2 が '1' になり、Q3 が '1' になり (1111) になるが、この場合は NAND によって直後にリセットが '0' になるため、すべてが (0000) に戻されまったく機能しなくなる。こういう現象を racing というがこれを防いでいる。もっとも負論理入力にしたらしたで、(1111) の状態でパルスが入ると racing が起きるわけなので本質的な解決はしていない。実際にカウンタを設計する人は注意して欲しい。

下図はディジタル技術検定 3 級第 51 回の (10) である。

タイミングチャートを見てどんな回路か当てるという問題だが、説明するのも難しいほど簡単な機能であり、入力信号が一クロック分遅れて出力されるというもので Delay Flip-flop = (3)D フリップフロップが正解である。が、J-K フリップフロップとインバータを使っても同等の機能を実現できるので、問題としてはどうかと思う。

下図はディジタル技術検定 3 級第 50 回の (10) である。

3 bit のシフトレジスタの問題である。タイミングチャートがいやがらせの如く左右逆に書いてあるため見づらいが、クリア = リセット = 出力をオール '0' にしたあと、タイミング b, c , d と推移していったあとどうなるかを考えれば良い。この場合はタイミング b では abc 順に (100) 、タイミング c では (010)、タイミング d では (101) になるということで、(3)が正解となる。なお先ほどいやがらせの如く左右逆と書いたが、答えとの方向は一致している。また仮に左右を間違えても同じ結果なのでサービス問題かも知れない。(110) が正解というような問題の出し方をされたら間違える人が増えそうである。

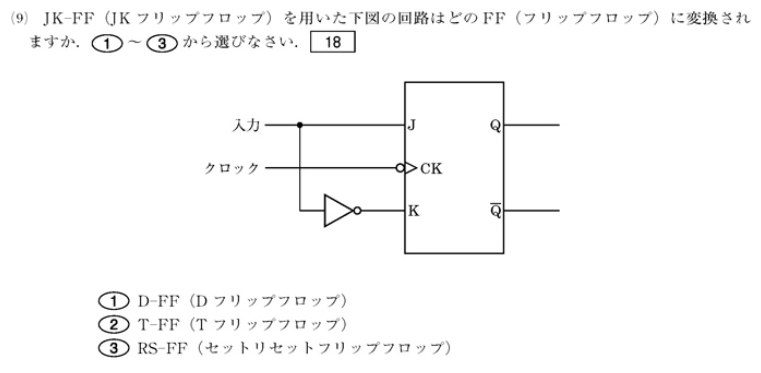

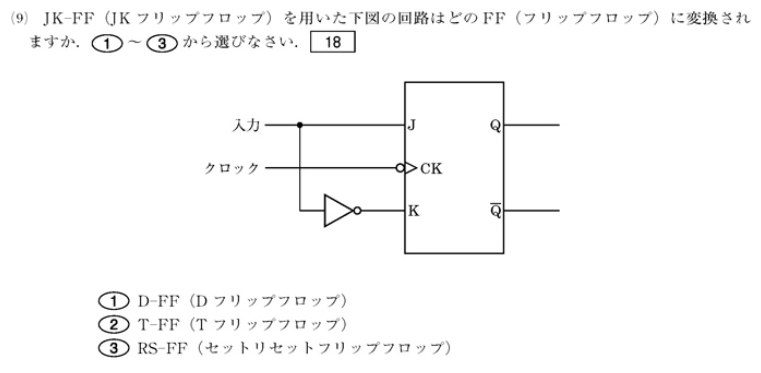

下図はディジタル技術検定 3 級第 48 回の (9) である。

JK - FF を応用例である。ここで使われる JK - FF の真理値表は以下のようになっている。

フリップフロップはいわゆるラッチと違って、入力の取り込みを CK(または CLK)と云われるクロックに同期して行われる。この場合は CK 端子の前に○がついているので、立ち下がりエッジに反応して入力の取り込みが行われ出力される。そのため上述の真理値表は一般的に見かける物に比べて記述が多い。普通はクリーム色の部分だけであろう。だが実際にはエッジで変化するというのは設計上重要な情報なのであえて載せておいた。

さて、こういう真理値表を持つ JK - FF を問題のような回路で使うとどうなるかを考える。ここでは K は強制的に J の反転(否定)なので、J K の両方が同じ値を持つことはない。よってクリーム色の 4 行のうちの真ん中の 2 行だけが使われていることになる。その後は見ての通り J = Q なので、これは入力値がそのまま遅れて出力される(1) D - FF(D フリップフロップ)が正解となる。

ちなみに J K の両方を '1' に固定しておくと、立ち下がりエッジが入る度に出力が反転する T - FF となる。

下図はディジタル技術検定 3 級第 47 回の (9) である。

最初に説明した第 52 回の (9) と比較すれば解説は不要だと思うので省略する。(2)端子 Y が正解である。

← にほんブログ村「科学」-「技術・工学」へ

← にほんブログ村「科学」-「技術・工学」へ

↑ クリックをお願いします。

フリップフロップ(Flip-Flop)を使った非同期カウンタの問題で、フリップフロップが 4 つあるのでいわゆる 4 bit カウンタである。

ここで使われているフリップフロップは T フリップフロップといって、T' 端子に下降信号(立ち下がりエッジ)が入ると出力が反転するものである。仮に 4 つのフリップフロップの初期値を (0000) とすると、一番左の入力パルスの立ち下がり信号が入ると Q0 が反転して '1' になる。他のフリップフロップの T' は変化していないので出力は変わらない。よって (0000) → (1000) と変化する(普通の表記と上位と下位が逆になっていることに注意)。次に入力パルスの立ち下がりがあると、Q0 は '0' になる。このためその右のフリップフロップには '1' から '0' に変化した信号が入力されるので、Q1 の出力は反転して '1' になる。Q2, Q3 は変化しないので、(0100) となる。以下同様にパルスを与えていくと、Q0, Q1, Q2, Q3 は順次変化していくが Q1 と Q3 が同時に '1' になると NAND を通して、各フリップフロップのリセット端子に '0' を出力して、Q0, Q1, Q2, Q3 をすべてリセット = (0000) にしてしまい、初期値に戻る。よって、(0000) から (0101) まで変化して元に戻るので、0 から 10 まで数えたところで 0 に戻るということで、(4)の 10 進カウンタが正解となる。0 から 10 なら 11 個数えたことになるのでは?と思うかも知れないが、(0101) となった瞬間に次のパルスが入る前に (0000) に戻ってしまうので、10 は数えたことにしない。変な感じだが、非同期カウンタはこういう動作をすることが多い。

参考までにタイミングチャートはこのようになる。(0101) になった期間が短くすぐに (0000) になっている。

余談だが、T が負論理 T' になっていて入力パルスの立ち下がりに反応するようになっているのは、もしこれを立ち上がりに反応するようにすると、Q0 が '1' になった瞬間にその立ち上がりに反応して Q1 が '1' になり、それを受けて Q2 が '1' になり、Q3 が '1' になり (1111) になるが、この場合は NAND によって直後にリセットが '0' になるため、すべてが (0000) に戻されまったく機能しなくなる。こういう現象を racing というがこれを防いでいる。もっとも負論理入力にしたらしたで、(1111) の状態でパルスが入ると racing が起きるわけなので本質的な解決はしていない。実際にカウンタを設計する人は注意して欲しい。

下図はディジタル技術検定 3 級第 51 回の (10) である。

タイミングチャートを見てどんな回路か当てるという問題だが、説明するのも難しいほど簡単な機能であり、入力信号が一クロック分遅れて出力されるというもので Delay Flip-flop = (3)D フリップフロップが正解である。が、J-K フリップフロップとインバータを使っても同等の機能を実現できるので、問題としてはどうかと思う。

下図はディジタル技術検定 3 級第 50 回の (10) である。

3 bit のシフトレジスタの問題である。タイミングチャートがいやがらせの如く左右逆に書いてあるため見づらいが、クリア = リセット = 出力をオール '0' にしたあと、タイミング b, c , d と推移していったあとどうなるかを考えれば良い。この場合はタイミング b では abc 順に (100) 、タイミング c では (010)、タイミング d では (101) になるということで、(3)が正解となる。なお先ほどいやがらせの如く左右逆と書いたが、答えとの方向は一致している。また仮に左右を間違えても同じ結果なのでサービス問題かも知れない。(110) が正解というような問題の出し方をされたら間違える人が増えそうである。

下図はディジタル技術検定 3 級第 48 回の (9) である。

JK - FF を応用例である。ここで使われる JK - FF の真理値表は以下のようになっている。

フリップフロップはいわゆるラッチと違って、入力の取り込みを CK(または CLK)と云われるクロックに同期して行われる。この場合は CK 端子の前に○がついているので、立ち下がりエッジに反応して入力の取り込みが行われ出力される。そのため上述の真理値表は一般的に見かける物に比べて記述が多い。普通はクリーム色の部分だけであろう。だが実際にはエッジで変化するというのは設計上重要な情報なのであえて載せておいた。

さて、こういう真理値表を持つ JK - FF を問題のような回路で使うとどうなるかを考える。ここでは K は強制的に J の反転(否定)なので、J K の両方が同じ値を持つことはない。よってクリーム色の 4 行のうちの真ん中の 2 行だけが使われていることになる。その後は見ての通り J = Q なので、これは入力値がそのまま遅れて出力される(1) D - FF(D フリップフロップ)が正解となる。

ちなみに J K の両方を '1' に固定しておくと、立ち下がりエッジが入る度に出力が反転する T - FF となる。

下図はディジタル技術検定 3 級第 47 回の (9) である。

最初に説明した第 52 回の (9) と比較すれば解説は不要だと思うので省略する。(2)端子 Y が正解である。

↑ クリックをお願いします。