前回、この回路設計を考えるに当たって考慮しなくてはいけない項目を挙げました。

再掲します。

・オペアンプのフィードバック回路の中に FET による電流バッファが入っていてかつ広帯域を要求されているのでその安定性。

・電流検出抵抗が 0.1Ωとなっているがその妥当性。あるいは値と性能との関係。

・FET のゲート電圧/ドレイン電流特性の線形性。もともとパワー FET はスイッチング用途なのでリニア用途に使った場合の問題点。

・ゲート容量とオペアンプの駆動能力。

・パルスがオフの時のオペアンプの挙動。

・オペアンプの DC 特性(オフセット電圧、入力バイアス電流)の影響。

まずは最初の項目から見ていきます。

昔の記事でこんなことを書いています。

電圧電流変換 → LED駆動回路

http://blogs.yahoo.co.jp/susanoo2001_hero/5354687.html

一方、こんなことも書いています。

もう少し伝達関数表現で考えてみた。>やさしく考えるアナログ回路

http://blogs.yahoo.co.jp/susanoo2001_hero/6036059.html

さらに、こんなことも書いています。

オペアンプの特性とフィードバック回路の影響

http://blogs.yahoo.co.jp/susanoo2001_hero/8197368.html

これらを組み合わせて考える必要があるのが、今回のテーマです。

要約すると、理想オペアンプを前提に付加回路を付け加えて必要な機能を実現するための回路構成を考えます。次に付加回路込みでどんな伝達特性になっているかを考えます。次に、オペアンプは理想的には動いてくれないので付加回路がフィードバックループにどんな影響与えるかを考えて必要あらば周波数特性の補償を考えます。という流れです。

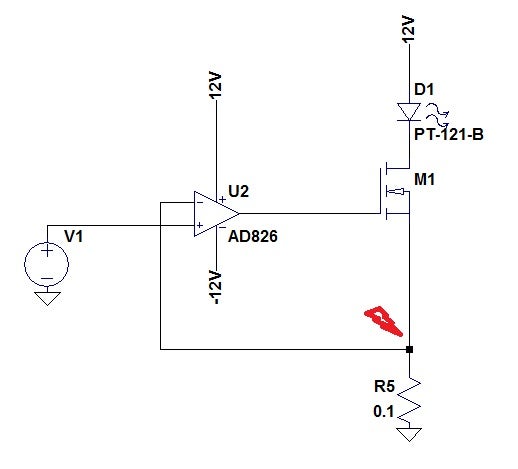

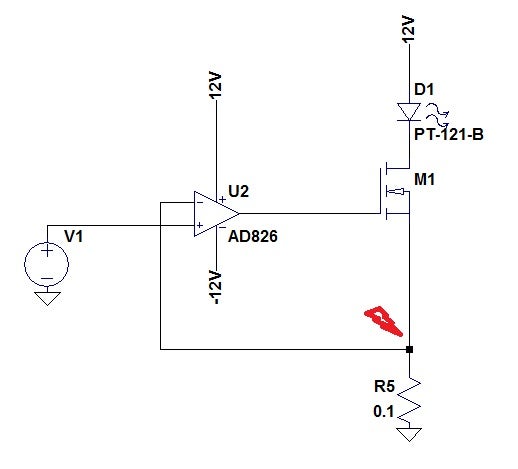

そうすると今回の回路の原型はこれになります。

実にシンプルです。各デバイスが理想的に動いてくれればまったく問題なく動きます。もちろんそうはいかないので、それぞれのデバイスの特性をチェックしながら回路を構築していきます。

最初はオペアンプの特性を調べてみましょう。実にシンプルな非反転バッファです。

周波数特性もこんな感じで良さげです。

パルス応答もこんな感じです。青が入力、緑が出力。

AD826 のゲイン交点付近での特性もこんな感じで位相マージンはありそうです。

ということで簡単にいくに違いない、と上図の回路で周波数特性を取ってみます。出力の測定点は FET のソースにある 0.1Ωのところです。

(上図赤い稲妻)

あれあれ 10MHz ぐらいでピークを持ってしまっているようです。

ついでにパルス応答も測定してみます。電流は 5A 流した場合です。

赤い線が抵抗の電流、緑色の線が入力パルスです。

拡大すると、

やはりというか立ち上がりでオーバーシュートが出ています。2 倍ぐらいのピークが 50ns 周期で出ていますから、周波数特性と合っているような無いようなですが。

これでは困りますので、原因を探し出して解決しなくてはいけません。

ちなみに 1MHz 正弦波の場合はこうです。

青色の線はオペアンプの出力です。電流がまともに反応しているのは最初の半周期でそれ以降は発狂状態です。簡単に言うと、出力電流は片方にしか流れないのでマイナスの入力電圧が入った場合はオペアンプのフィードバックはオープンになってしまうので異常状態になります。

反省して、入力にオフセットを与えるとこんな感じでちゃんと動きます。

では先ほどのパルス応答で少し入力信号の "Low" 側にマイナス電位を与えてみます。

なんか見たくない波形になりました。

これも簡単に解説しておくと、入力信号の "Low" がマイナス電位になっているとオペアンプのフィードバックループがオープンになるため、オペアンプの出力がマイナス側に張り付きます。そのため "High" になったときにそこからの脱出に時間が掛かっているというわけです。

戻って最初のシミュレーションではそのようなことは発生していなかったので、違う問題と考えておきます。

回路構成してはオペアンプに FET による電流バッファがつながっている形ですので、この FET 電流バッファの特性を調べておきます。

FET はゲートに掛かる電圧に従って、ドレイン電流=ソース電流が変わるというものです。この特性を見ておきましょう。

測定回路はこれです。

DC 特性はこれです。

2.5V ぐらいから電流が流れだして、2.7V ぐらいで飽和する、というようです。

拡大しておきます。

さて、実際に使いたいのは 1A ~ 10A ということなので、カーブをよく見てみますと、1A 以下では傾きが寝ています。2A 以降は傾きがほぼ等しいです。これはどういうことかというとゲート電圧はオペアンプの出力ですから、FET の電流値を何らかの形で検出してオペアンプに戻してフィードバックを掛けようとした場合、そのフィードバックゲインが流す電流によって変動すると云うことです。このことは理想オペアンプでは考える必要は無いですし、低速のオペアンプの場合もほとんど考える必要はありません。ですが今回は広帯域を確保して高速応答をさせたいわけですから、オペアンプの能力のぎりぎりで使うことになり、フィードバックゲインの変動は気になるかも知れません。

ちなみに上述の特性から、1A 付近の傾きと 5A 付近の傾きの違いは 1.5 倍ぐらいあります。

念のため周波数特性も見ておきます。ゲート電圧に対するドレイン電流の特性です。

注意しておかなくてはいけないのは、ゲート電圧は上述の範囲でないと動作しませんので信号源に適当にオフセットを与えておきます。

振幅も小さくしておきます。

数MHz ぐらいの帯域ですかね。なんか物足りない気はしますが。

ちなみにこの FET はトピ主が使っているものではありません。Spice データがないので似たようなものを探してきただけです。

しかし、実際にはソースに抵抗 0.1Ωが入っています。この影響も見ておきましょう。

回路図はこれです。

DC 特性です。今回はドレイン電流と 0.1Ωの電位も表示しました。

入力電圧に対してリニアな領域が増えています。傾斜も緩やかになっています。これはこちらを思い出して下さい。

やさしく考えるアナログ回路: トランジスタのリニア動作

http://blogs.yahoo.co.jp/susanoo2001_hero/7013492.html

ここでトランジスタの場合ですが、エミッタに抵抗が入ったらリニア動作と考えましょう、としていますが、FET の場合も同じです。むしろ FET の場合の方が考えやすいです。

つまり、ソースに抵抗があるためゲート電圧が上昇してドレイン電流が上昇するとソース抵抗に流れる電流が増えるためソース電位が上がります。そのためゲート vs ソース間の電位差が下がって適当なところでドレイン電流が抑制されるからです。

拡大図です。

抵抗がないときに比べて、直線性が良くなっています。1A と 5A で直線の傾きは 1.2 倍に収まっています。もう一つありがたいことに、ゲート電圧と変化 vs 抵抗の電位の比が 0.6 ~ 0.8 と 1 以下になっていることです。これはどういうことかというと、オペアンプの出力電圧変化が抵抗のところでは変化率が減少=電圧利得が減少していることです。

なんでありがたいかというと、ただでさえ高速オペアンプはユニティゲイン= 100% 帰還で使うと不安定になりがちなのでフィードバックゲインを下げてくれるのは動作の安定性に貢献してくれます。もっともこの抵抗値を上げれば上げるほど電圧利得は 1 に近づくだけなのであまり問題にはなりませんが。というかむしろ抵抗値が高い方が動作状態に関係なくフィードバックゲインの一定になるので、設計的には本当はそちらのほうが良いです。

この FET における電圧フィードバックゲインのカラクリを計算しておきます。

ここで Yft というのは、Vgs に対する Id の変換利得です。前のグラフの傾き相当します。1A では 75、5A では 130 ぐらいでした。

この式から Vft と R 積が大きければ大きいほど、(Vout / Vin) は 1 に近づきます。

戻ってこの FET 電流バッファの周波数特性はというと、こんな感じです。(中心電圧 4V)

傾斜が緩やかになった分、利得は落ちて帯域が広がりました。

ですが、やはり目標は広帯域なので 数十MHz ぐらいは余裕で通過させないとオペアンプのゲイン交点付近での位相遅れに FET + 0.1Ω の位相遅れが加算されますので、応答が悪くなります。

だいたいですが検討してみると、AD826 のゲイン交点は約 50MHz ぐらい。それに対して FET + 0.1Ω によるゲインロスは、- 5.6dB ぐらいです。トータルでゲイン交点は 50MHz / (5.6dB)で約 30MHz。その時のオペアンプの位相マージンは 85°ぐらい。これに加えて FET + 0.1Ωが 30MHz で 21°の遅れがあるので、位相マージンが 64°とちょっとピークを持つような特性になってきます。

その他にオペアンプと FET + 0.1Ω の接続間で多少の位相遅れや減衰が発生すると思います。

結局、それやこれやで、パルスとしてはオーバーシュートを発生させてしまうので対策が必要になります。

← にほんブログ村「科学」-「技術・工学」へ

← にほんブログ村「科学」-「技術・工学」へ

↑ クリックをお願いします。

再掲します。

・オペアンプのフィードバック回路の中に FET による電流バッファが入っていてかつ広帯域を要求されているのでその安定性。

・電流検出抵抗が 0.1Ωとなっているがその妥当性。あるいは値と性能との関係。

・FET のゲート電圧/ドレイン電流特性の線形性。もともとパワー FET はスイッチング用途なのでリニア用途に使った場合の問題点。

・ゲート容量とオペアンプの駆動能力。

・パルスがオフの時のオペアンプの挙動。

・オペアンプの DC 特性(オフセット電圧、入力バイアス電流)の影響。

まずは最初の項目から見ていきます。

昔の記事でこんなことを書いています。

電圧電流変換 → LED駆動回路

http://blogs.yahoo.co.jp/susanoo2001_hero/5354687.html

一方、こんなことも書いています。

もう少し伝達関数表現で考えてみた。>やさしく考えるアナログ回路

http://blogs.yahoo.co.jp/susanoo2001_hero/6036059.html

さらに、こんなことも書いています。

オペアンプの特性とフィードバック回路の影響

http://blogs.yahoo.co.jp/susanoo2001_hero/8197368.html

これらを組み合わせて考える必要があるのが、今回のテーマです。

要約すると、理想オペアンプを前提に付加回路を付け加えて必要な機能を実現するための回路構成を考えます。次に付加回路込みでどんな伝達特性になっているかを考えます。次に、オペアンプは理想的には動いてくれないので付加回路がフィードバックループにどんな影響与えるかを考えて必要あらば周波数特性の補償を考えます。という流れです。

そうすると今回の回路の原型はこれになります。

実にシンプルです。各デバイスが理想的に動いてくれればまったく問題なく動きます。もちろんそうはいかないので、それぞれのデバイスの特性をチェックしながら回路を構築していきます。

最初はオペアンプの特性を調べてみましょう。実にシンプルな非反転バッファです。

周波数特性もこんな感じで良さげです。

パルス応答もこんな感じです。青が入力、緑が出力。

AD826 のゲイン交点付近での特性もこんな感じで位相マージンはありそうです。

ということで簡単にいくに違いない、と上図の回路で周波数特性を取ってみます。出力の測定点は FET のソースにある 0.1Ωのところです。

(上図赤い稲妻)

あれあれ 10MHz ぐらいでピークを持ってしまっているようです。

ついでにパルス応答も測定してみます。電流は 5A 流した場合です。

赤い線が抵抗の電流、緑色の線が入力パルスです。

拡大すると、

やはりというか立ち上がりでオーバーシュートが出ています。2 倍ぐらいのピークが 50ns 周期で出ていますから、周波数特性と合っているような無いようなですが。

これでは困りますので、原因を探し出して解決しなくてはいけません。

ちなみに 1MHz 正弦波の場合はこうです。

青色の線はオペアンプの出力です。電流がまともに反応しているのは最初の半周期でそれ以降は発狂状態です。簡単に言うと、出力電流は片方にしか流れないのでマイナスの入力電圧が入った場合はオペアンプのフィードバックはオープンになってしまうので異常状態になります。

反省して、入力にオフセットを与えるとこんな感じでちゃんと動きます。

では先ほどのパルス応答で少し入力信号の "Low" 側にマイナス電位を与えてみます。

なんか見たくない波形になりました。

これも簡単に解説しておくと、入力信号の "Low" がマイナス電位になっているとオペアンプのフィードバックループがオープンになるため、オペアンプの出力がマイナス側に張り付きます。そのため "High" になったときにそこからの脱出に時間が掛かっているというわけです。

戻って最初のシミュレーションではそのようなことは発生していなかったので、違う問題と考えておきます。

回路構成してはオペアンプに FET による電流バッファがつながっている形ですので、この FET 電流バッファの特性を調べておきます。

FET はゲートに掛かる電圧に従って、ドレイン電流=ソース電流が変わるというものです。この特性を見ておきましょう。

測定回路はこれです。

DC 特性はこれです。

2.5V ぐらいから電流が流れだして、2.7V ぐらいで飽和する、というようです。

拡大しておきます。

さて、実際に使いたいのは 1A ~ 10A ということなので、カーブをよく見てみますと、1A 以下では傾きが寝ています。2A 以降は傾きがほぼ等しいです。これはどういうことかというとゲート電圧はオペアンプの出力ですから、FET の電流値を何らかの形で検出してオペアンプに戻してフィードバックを掛けようとした場合、そのフィードバックゲインが流す電流によって変動すると云うことです。このことは理想オペアンプでは考える必要は無いですし、低速のオペアンプの場合もほとんど考える必要はありません。ですが今回は広帯域を確保して高速応答をさせたいわけですから、オペアンプの能力のぎりぎりで使うことになり、フィードバックゲインの変動は気になるかも知れません。

ちなみに上述の特性から、1A 付近の傾きと 5A 付近の傾きの違いは 1.5 倍ぐらいあります。

念のため周波数特性も見ておきます。ゲート電圧に対するドレイン電流の特性です。

注意しておかなくてはいけないのは、ゲート電圧は上述の範囲でないと動作しませんので信号源に適当にオフセットを与えておきます。

振幅も小さくしておきます。

数MHz ぐらいの帯域ですかね。なんか物足りない気はしますが。

ちなみにこの FET はトピ主が使っているものではありません。Spice データがないので似たようなものを探してきただけです。

しかし、実際にはソースに抵抗 0.1Ωが入っています。この影響も見ておきましょう。

回路図はこれです。

DC 特性です。今回はドレイン電流と 0.1Ωの電位も表示しました。

入力電圧に対してリニアな領域が増えています。傾斜も緩やかになっています。これはこちらを思い出して下さい。

やさしく考えるアナログ回路: トランジスタのリニア動作

http://blogs.yahoo.co.jp/susanoo2001_hero/7013492.html

ここでトランジスタの場合ですが、エミッタに抵抗が入ったらリニア動作と考えましょう、としていますが、FET の場合も同じです。むしろ FET の場合の方が考えやすいです。

つまり、ソースに抵抗があるためゲート電圧が上昇してドレイン電流が上昇するとソース抵抗に流れる電流が増えるためソース電位が上がります。そのためゲート vs ソース間の電位差が下がって適当なところでドレイン電流が抑制されるからです。

拡大図です。

抵抗がないときに比べて、直線性が良くなっています。1A と 5A で直線の傾きは 1.2 倍に収まっています。もう一つありがたいことに、ゲート電圧と変化 vs 抵抗の電位の比が 0.6 ~ 0.8 と 1 以下になっていることです。これはどういうことかというと、オペアンプの出力電圧変化が抵抗のところでは変化率が減少=電圧利得が減少していることです。

なんでありがたいかというと、ただでさえ高速オペアンプはユニティゲイン= 100% 帰還で使うと不安定になりがちなのでフィードバックゲインを下げてくれるのは動作の安定性に貢献してくれます。もっともこの抵抗値を上げれば上げるほど電圧利得は 1 に近づくだけなのであまり問題にはなりませんが。というかむしろ抵抗値が高い方が動作状態に関係なくフィードバックゲインの一定になるので、設計的には本当はそちらのほうが良いです。

この FET における電圧フィードバックゲインのカラクリを計算しておきます。

ここで Yft というのは、Vgs に対する Id の変換利得です。前のグラフの傾き相当します。1A では 75、5A では 130 ぐらいでした。

この式から Vft と R 積が大きければ大きいほど、(Vout / Vin) は 1 に近づきます。

戻ってこの FET 電流バッファの周波数特性はというと、こんな感じです。(中心電圧 4V)

傾斜が緩やかになった分、利得は落ちて帯域が広がりました。

ですが、やはり目標は広帯域なので 数十MHz ぐらいは余裕で通過させないとオペアンプのゲイン交点付近での位相遅れに FET + 0.1Ω の位相遅れが加算されますので、応答が悪くなります。

だいたいですが検討してみると、AD826 のゲイン交点は約 50MHz ぐらい。それに対して FET + 0.1Ω によるゲインロスは、- 5.6dB ぐらいです。トータルでゲイン交点は 50MHz / (5.6dB)で約 30MHz。その時のオペアンプの位相マージンは 85°ぐらい。これに加えて FET + 0.1Ωが 30MHz で 21°の遅れがあるので、位相マージンが 64°とちょっとピークを持つような特性になってきます。

その他にオペアンプと FET + 0.1Ω の接続間で多少の位相遅れや減衰が発生すると思います。

結局、それやこれやで、パルスとしてはオーバーシュートを発生させてしまうので対策が必要になります。

↑ クリックをお願いします。