パワー半導体の開発にもEDA、三菱電機が試作回数削減へ

小島 郁太郎

日経クロステック/日経エレクトロニクス

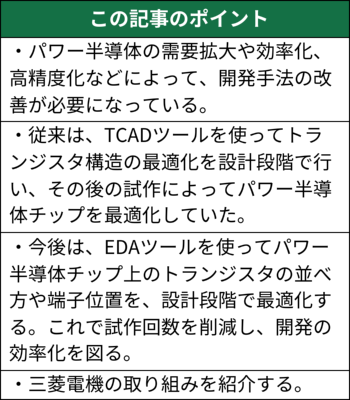

地球環境保護や気候変動対策としてパワー半導体への期待は高まる一方である。期待に応えようとパワー半導体の効率化(小型化かつ大容量化)を狙い、その開発手法が変わってきた。従来は、もっぱらトランジスタの特性最適化に力が注がれていた。最近では、多数のトランジスタを集積したパワー半導体チップや、同チップを搭載したパワー半導体モジュールの最適化も欠かせなくなっている。この記事では、三菱電機がEDA(Electronic Design Automation)ツールを活用して、パワー半導体チップの最適化を進めている事例を紹介する(図1)。

図1 パワー半導体の開発手法について講演する三菱電機の原田 辰雄氏

(出所:ジーダットのユーザー向けイベントにおいて、同社が撮影)

[画像のクリックで拡大表示]

従来、パワー半導体の開発では、トランジスタの最適設計を狙ってTCAD(Technology Computer Aided Design)ツールが使われてきた。TCADには主に2種類がある。トランジスタ形成に最適なプロセス条件を探るために使うプロセスシミュレーターと、トランジスタ特性を最適化するトランジスタの構造を探るために使うデバイスシミュレーターである。例えば、日経クロステックでは、東芝デバイス&ストレージとジャパンセミコンダクターが、車載向け高耐圧LDMOS(Laterally Double Diffused MOS)トランジスタの開発でTCADを活用した事例を紹介している

一般にパワー半導体のチップ(ダイ)には、所望の耐圧や増幅率を実現するために多数のトランジスタ(通常は、同じ構造のトランジスタ)が集積されている。このため、チップ上のトランジスタの配置や端子位置(例えば、ボンディングワイヤとの接続点)は、チップ最適化に影響する。かつては、こうしたチップレベルの最適化は試作を繰り返して行うケースが多かった。微細なプロセスで造る最先端マイクロプロセッサーに比べれば、試作コストが小さいことなどがその背景にある。

最近は、パワー半導体の需要拡大や、効率化や高精度化などといった要求仕様の高度化によって、開発手法の改善が必要になっている。例えば、EDAツールを使って、チップレベルの最適化を行い、試作回数を減らしたり、限りなくゼロに近づけたりする。日経クロステックでは、ルネサス エレクトロニクスがEDAツール使ってチップ内のトランジスタの配置を開発の早い段階(フロアプラン段階)で決めることにより、開発期間全体を短縮する事例を紹介した。その事例では米Synopsys(シノプシス)のアナログ/カスタムIC設計用EDAツール「Custom Compiler」を使っており、日本シノプシスが主催したユーザー向けイベントにおいてルネサス エレクトロニクスのエンジニアが講演している

パワー半導体の開発にもEDA、三菱電機が試作回数削減へ | 日経クロステック(xTECH) (nikkei.com)

==================================

半導体の製造技術だけでは勝てない時代、日本企業も設計で奮闘

小島 郁太郎

日経クロステック/日経エレクトロニクス

Rapidus(ラピダス、東京・千代田)の登場によって、半導体への世間の関心は、日本の半導体産業が絶好調だった1980年代後半に匹敵するほどになった。その1980年代後半において、半導体プロセス(製造技術)の微細化をいち早く進めることが、最重要事項だった。実際、半導体の設計を担当する駆け出しの記者だった筆者に、ある国内半導体メーカーのエンジニアはこう教えてくれた。「設計で工夫して多少性能を上げるよりも、微細なプロセスへ早く移行すれば、性能は楽に上げられる」。この考え方は現在も変わっていないようで、ラピダスが打ち出した「世界最先端の2nm世代プロセスの工場を建てる」という計画は世間や政府を魅了した。

プロセスがなければ半導体が造れないことは、40年前も現在も変わらない。ただし最近は微細化のピッチが大きく鈍ってきており、「微細化といようよりも、様々な工夫を積み重ねて何とかプロセス世代を進めているのが本当のところ」(ある米国半導体メーカー日本法人のエンジニア)という。その様々な工夫の中で、40年前に比べて比重がぐんと高くなっているのが設計技術である。

例えば、2nm世代のような超微細なプロセスを使って競争力のある半導体を開発するには、製造が頑張っただけでは難しく、設計と製造が密に連携して最適化を進める「DTCO:Design Technology Co-Optimization(Technologyが製造に相当)」が欠かせない*1。微細化ピッチ鈍化の救世主といわれるヘテロジニアスインテグレーション(様々なチップレットを先端実装技術で1パッケージに収めること)にしても、設計の役割は重要だ*2。例えば、複数のチップレットへの回路の割り付け設計がまずいと、1チップに比べて性能が大きくダウンしたり、局所的な発熱によって素子を破壊してしまう危険があったりする。また一般的な半導体でも、開発品種数を増やしたい、開発期間(市場投入までの期間)を短縮したいなどの要求が高まっており、設計技術の高度化が欠かせなくなっている

最新の設計技術を国内で知る良い機会は、EDAツールベンダーの日本法人が開くプライベートイベントである。EDAはElectronic Design Automationの略で、EDAツールは半導体や基板(ヘテロジニアスインテグレーションのパッケージ基板や、プリント回路基板)といった電子回路の設計に使うソフトウエアを指す。プライベートイベントではEDAベンダーがEDAツールの最新情報を発表するほか、EDAツールのユーザー(すなわち半導体や基板の設計者)が講演する。ユーザーの講演は興味深い。実際の設計に適用された新しい技術が披露されることが多いからだ。日経クロステックでは、昨年(2023年)、日本ケイデンス・デザイン・システムズ社のイベントからソニーセミコンダクタソリューションズおよびキヤノンの講演*3を、シーメンスEDAジャパンのイベントからデンソーの講演*4を記事として紹介した。そして、本記事では、2023年9月に開催された米国Synopsysの日本法人である日本シノプシスのイベントから2件のユーザー講演のポイントを紹介する